# <u>for the X-Vertex Trigger</u> for the H1 Detector at HERA

May 1988

Diploma Thesis of Stefan Eichenberger

made in the group of Prof. Dr. P. Truöl under supervision of Dr. U. Straumann

Institute of Physics University of Zurich Schönberggasse 9 8001 Zurich

# Contents

| Coı | ntents<br>List of Tables<br>List of Figures                                                                                                                                                                                                                                                        | 1<br>3<br>3                                              |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|     | stract<br>sammenfassung                                                                                                                                                                                                                                                                            | 5<br>6                                                   |

| 1.  | Introduction 1.1 HERA and H1 1.2 Trigger Considerations                                                                                                                                                                                                                                            | 7<br>7<br>9                                              |

| 2.  | The z-Vertex Trigger 2.1 Overview 2.2 Simulations of the z-Vertex Trigger 2.2.1 Event Data 2.2.2 Trigger Algorithms 2.2.3 Definition of a Ray 2.2.4 Simulation Results 2.2.4.1 Phi Segmentation 2.2.4.2 Real Chambers 2.2.4.3 Eight Phi Segments 2.2.4.4 Parameters of the Peak Search Algorithm   | 11<br>11<br>15<br>15<br>18<br>18<br>22<br>22<br>25<br>26 |

|     | 2.3 Chamber Geometry 2.3.1 Pad Sizes 2.3.2 Simulations of Various Detector Geometries 2.3.3 Simulations of Various Ray Finder Algorithms 2.4 Big Tower Signals for Calorimeter Triggers                                                                                                            | 27<br>27<br>28<br>30                                     |

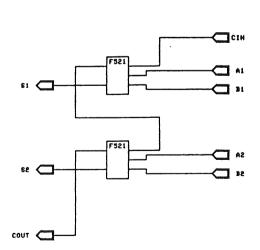

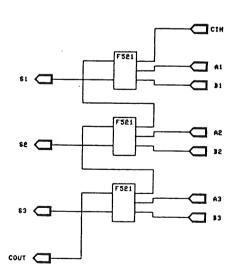

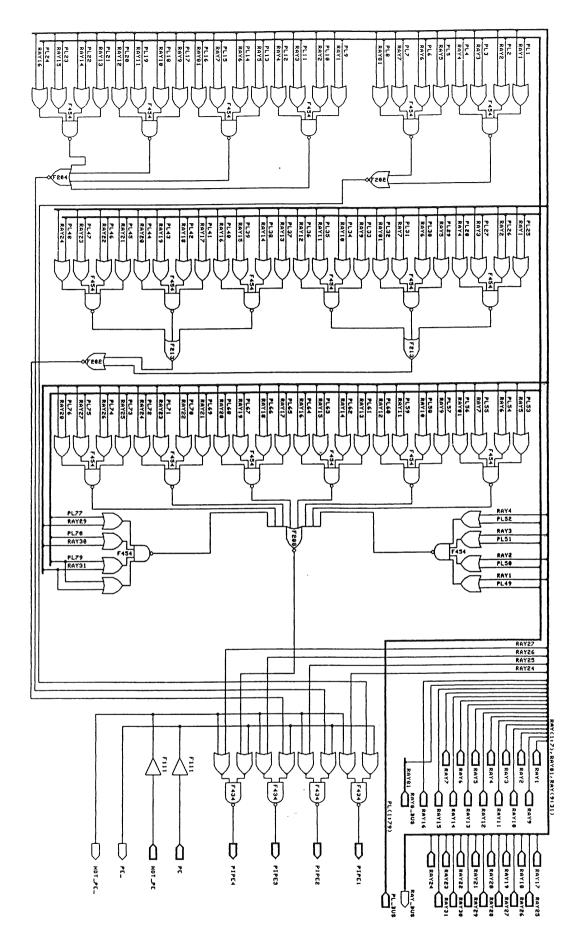

|     | Realization of the Ray Finder 3.1 Problem Description 3.2 Alternative Ray Finder Designs 3.3 The Gate Array Solution 3.4 The Gate Array Circuitry 3.4.1 The Block Scheme 3.4.2 The '3 out of 4' Option 3.4.3 The Mode Control Bit, Programming and General Purpose Applications for the Gate Array | 31<br>35<br>35<br>36<br>40<br>43<br>43<br>46<br>47       |

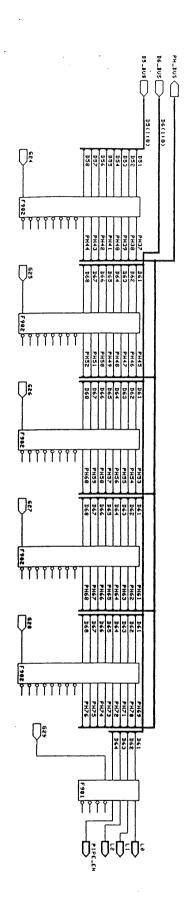

|     | 3.4.4 Use of the Gate Array for Generation of Big Tower Signals 3.5 The Ray Finder Printed Circuit Board                                                                                                                                                                                           | 49<br>50                                                 |

|     | 3.5.1 The Block Scheme 3.5.2 Realization of the Ray Finder PCBs 3.5.3 Timing Considerations 3.6 Test Equipment                                                                                                                                                                                     | 50<br>52<br>56<br>58                                     |

|     | O.V. LGAT. BUULDMEHL                                                                                                                                                                                                                                                                               | ~ ×                                                      |

| 4. Gate Array Development: Timing Considerations        | 6   |

|---------------------------------------------------------|-----|

| 4.1 Design Phase                                        | 6   |

| 4.2 Testing the Engineering Samples                     | 65  |

| 4.2.1 Power Consumption                                 | 69  |

| 4.2.2 AC Characteristics of the Pipeline                | 66  |

| 4.2.3 AC Characteristics of the Adder Cascade           | 61  |

| 4.2.4 Temperature and Supply Voltage                    | 68  |

| Dependencies                                            |     |

| 4.2.5 Conclusion                                        | 69  |

| Appendices                                              | 7:  |

| Appendix A: First Ideas for a Gate Array                | 7:  |

| Appendix B: NEC CMOS Gate Array Product Spectrum        | 74  |

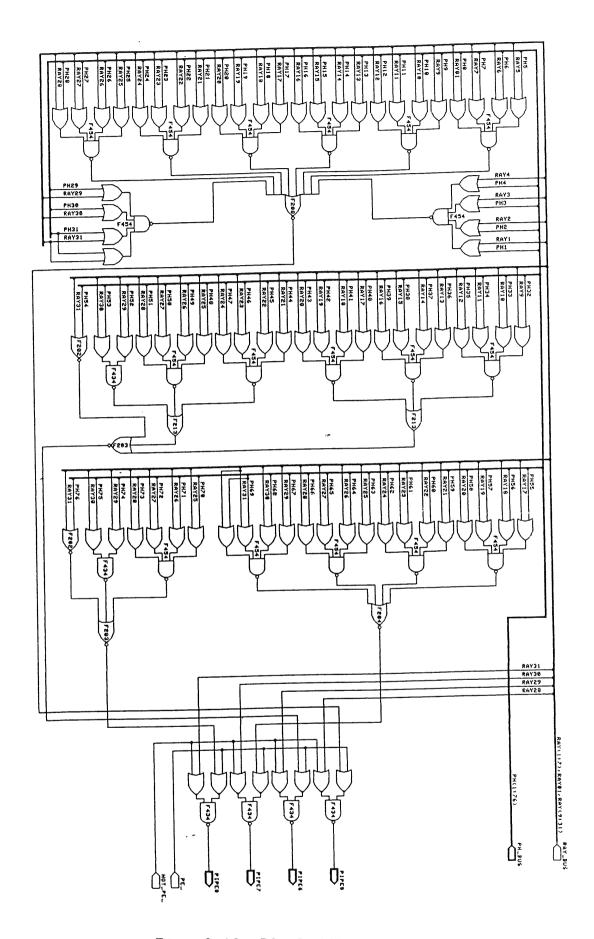

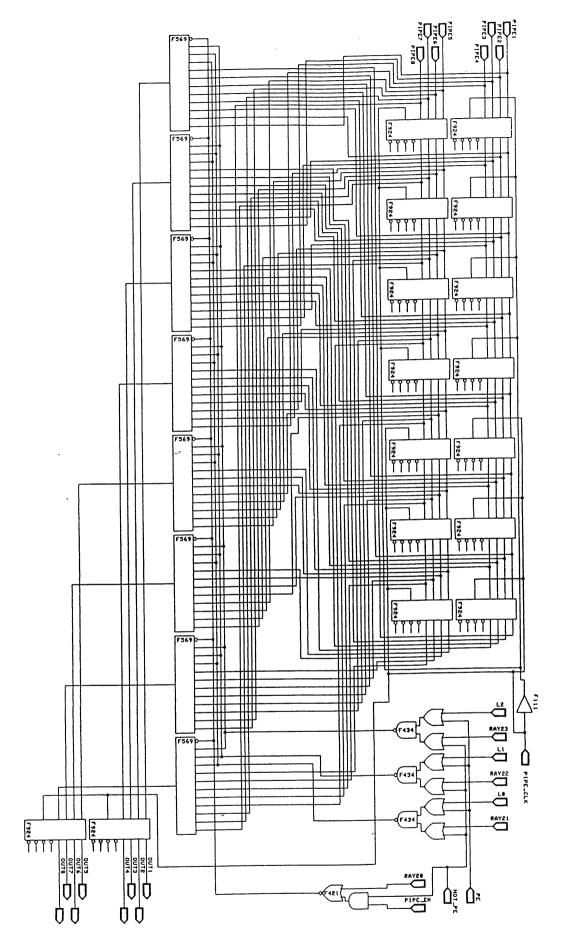

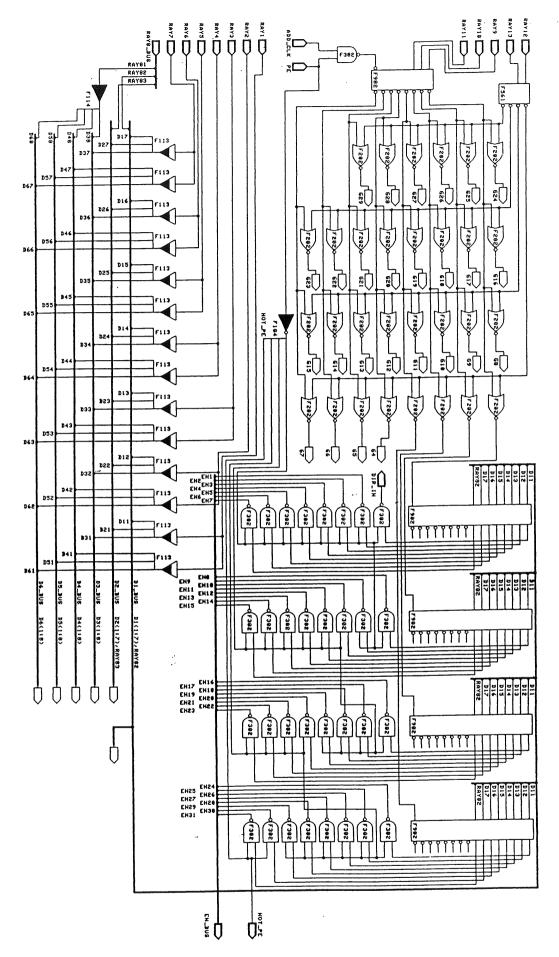

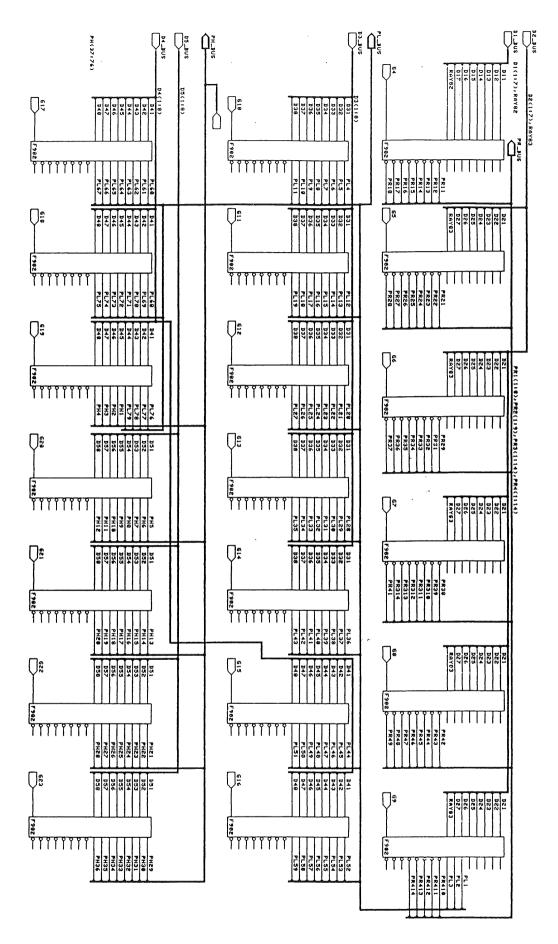

| Appendix C: Gate Array Schemes                          | 75  |

| Appendix D: Programmable Bits of the Gate Array         | 86  |

| Appendix E: Ray Allocation for the Ray Finder Prototype | 89  |

| Appendix F: Project Description for the                 | 96  |

| Gate Array                                              |     |

| Dictionary of Abbreviations                             | 101 |

| Bibliography                                            | 102 |

# <u>List of Tables</u>

| Table 2.1 Table 2.2 Table 2.3 Table 2.4                                                      | Simulated events data Chamber geometry z-vertex trigger simulation Influence of peak search algorithm parameters                                                                                                                                        | 16<br>20<br>23<br>27                         |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Table 2.5<br>Table 2.6<br>Table 2.7                                                          | Influence of chamber geometry<br>Various ray finder algorithms<br>Trigger bins                                                                                                                                                                          | 29<br>31<br>32                               |

| Table 3.1 Table 3.2 Table 3.3 Table 3.4 Table 3.5 Table 3.6                                  | Alternative ray finder designs CMOS gate arrays versus FAST TTL Ray and pin allocation for the gate array General purpose applications Power requirements of the ray finder Formulas concerning the ray finder timing                                   | 37<br>41<br>45<br>48<br>55<br>57             |

| Table 4.1<br>Table 4.2                                                                       | Supply voltage dependency<br>Temperature dependency                                                                                                                                                                                                     | 68<br>68                                     |

| List of Fig                                                                                  | ures                                                                                                                                                                                                                                                    |                                              |

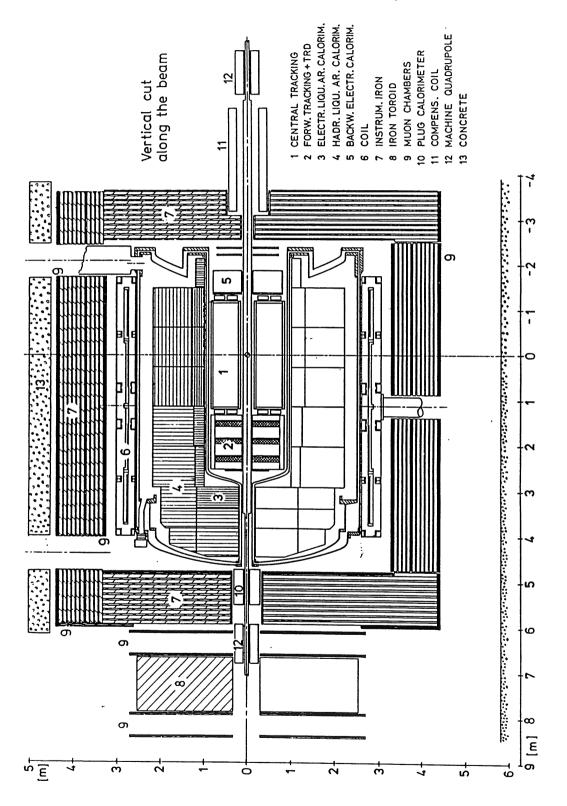

| Fig. 1.1                                                                                     | H1 detector layout                                                                                                                                                                                                                                      | 8                                            |

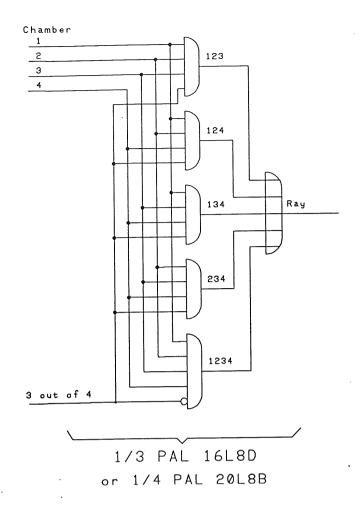

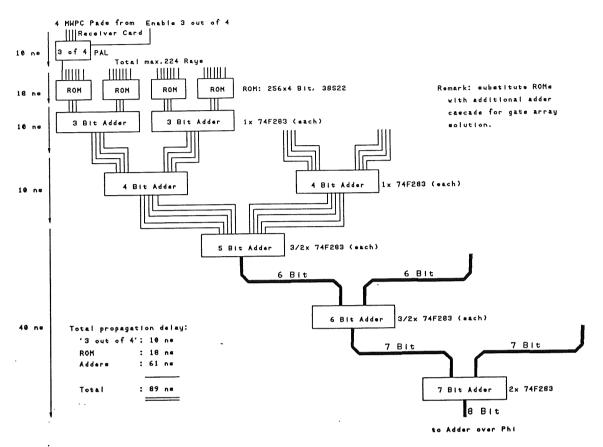

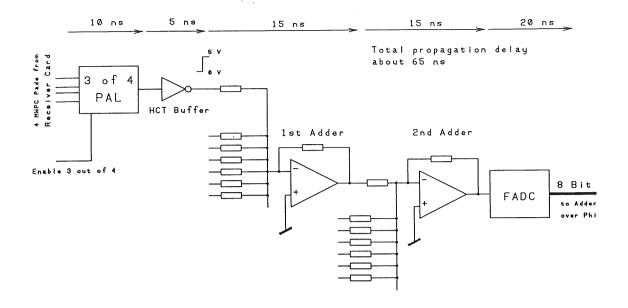

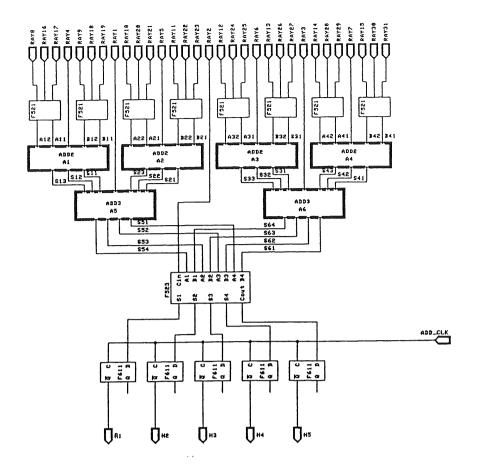

| Fig. 2.1<br>Fig. 2.2<br>Fig. 2.3<br>Fig. 2.4<br>Fig. 2.5<br>Fig. 2.6<br>Fig. 2.7             | H1 first level track trigger MWPCs used in the z-vertex trigger Examples of z-vertex histograms Cross-section of a MWPC Ray definition z-vertex histograms of random patterns Generation of big tower signals                                           | 12<br>13<br>17<br>19<br>21<br>30<br>33       |

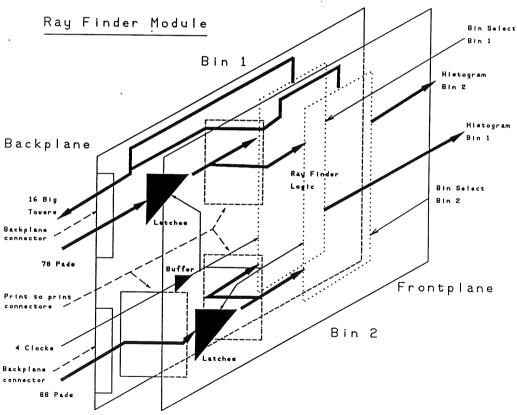

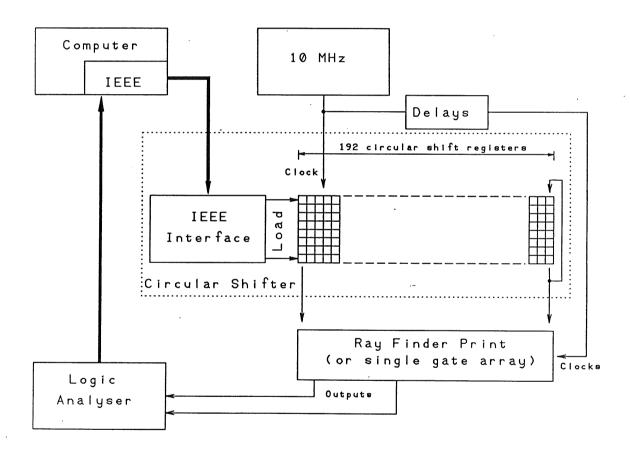

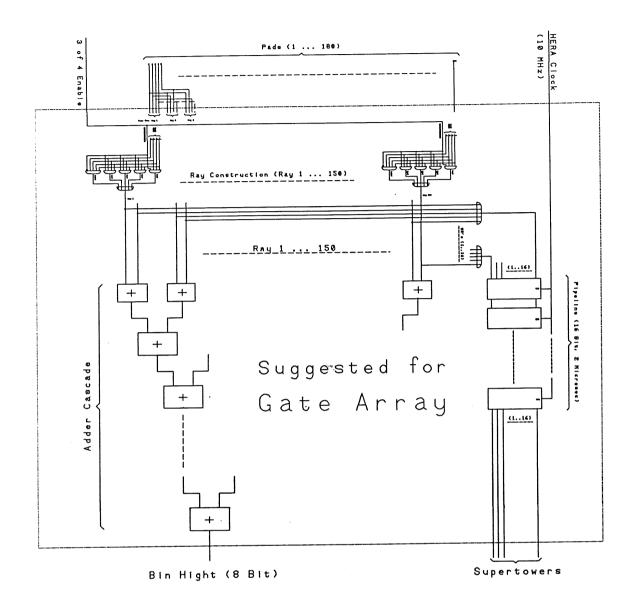

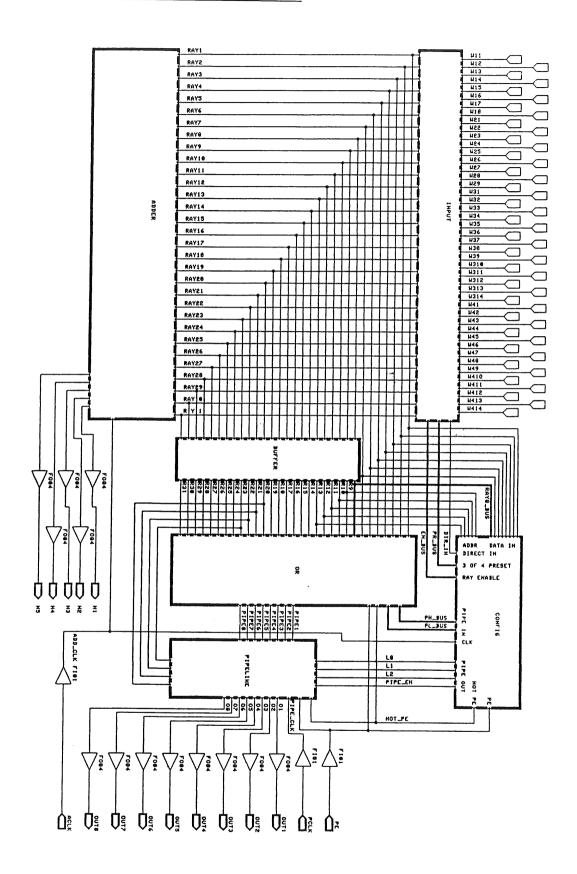

| Fig. 3.1<br>Fig. 3.2<br>Fig. 3.3<br>Fig. 3.4<br>Fig. 3.5<br>Fig. 3.6<br>Fig. 3.7<br>Fig. 3.8 | '3 out of 4' with PALs Ray finder with standard TTL ICs Analog solution for the ray finder Gate array block scheme Float diagram of the gate array Ray finder PCB block scheme Mechanical setup of the ray finder Test circuitry for the ray finder PCB | 38<br>39<br>40<br>44<br>49<br>51<br>53<br>59 |

|--|

## Abstract

For the first trigger level of the H1 detector at HERA, a z-vertex trigger has been suggested. Using fast multi wire proportional chamber signals, it should reconstruct the vertex location of an event along the beam axis. This report is concerned with the realization of the so called ray finder card, which recognizes rays in the data coming from six pairs of parallel planes of MWPCs. Together with the (not yet developed) vertex finder card, it forms the z-vertex trigger.

Chapter 2 describes various simulations made to test different setups for the ray finder and the influence of several suggestions for the exact geometry of the MWPCs. Input for these simulations were data obtained from Lund Monte Carlo simulations of neutral as well as charged current events.

Chapter 3 is concerned with the realization of the ray finder and shows that an application specific integrated circuit (a gate array) provides the best solution. This was dictated not only by technical but also economical reasons. Indications are given on how the gate array could be used for other applications as well.

Chapter 4 deals with timing constraints for the gate array and presents test results of measurements made on the engineering samples, which met all requirements well.

# Zusammenfassung

Als Teil der ersten Trigger Stufe für den H1 Detektor am HERA wurde ein z-Vertex Trigger vorgeschlagen. Unter Verwendung schneller Proportionalkammersignale soll er die Lage des Vertex auf der Strahlachse rekonstruieren. Diese Arbeit befasst sich mit der Entwicklung der sogenannten 'Ray Finder Card', die die Daten von sechs Kammerpaaren zu sogenannten 'Rays' verknüpft. Zusammen mit einer später zu entwickelnden 'Vertex Finder Card' bildet sie den z-Vertex Trigger.

)

Kapitel 2 beschreibt verschiedene Simulationen, die dazu dienen sollen. Varianten für den 'Ray Finder' und für die exakte Geometrie der Kammern zu testen. Die Simulationen beruhen auf Daten aus Lund Monte Carlo Rechnungen für Ereignisse mit neutralen und geladenen Strömen.

Kapitel 3 befasst sich mit der Planung des 'Ray Finders' und zeigt, dass die Entwicklung einer kundenspezifischen integrierten Schaltung (eines Gate Array) die beste Lösung des Problems darstellt. Hierfür sprechen sowohl technische wie wirtschaftliche Gründe. Gezeigt wird ebenfalls, wie der schlussendlich entwickelte IC in anderen Applikationen Verwendung finden könnte.

Kapitel 4 behandelt Ueberlegungen betreffs des Zeitverhaltens des Gate Arrays und präsentiert Resultate von Messungen, die an den Entwicklungsmustern vorgenommen wurden. Sie entsprechen allen Anforderungen.

# 1. Introduction

#### 1.1 HERA and H1

HERA is a new electron-proton collider currently under construction at DESY in Hamburg and due to be operational in 1990. The storage ring with a radius of about 800 m lets 30 GeV electrons collide with 820 GeV protons. Their respective tracks cross at two places, where international collaborations of about 25 universities and institutes each build complex particle detectors. One is called ZEUS, the University of Zurich collaborates in the H1 group.

With these particle energies a momentum transfer up to  $0^2 \approx 3*10^4 \text{ GeV}^2 \text{ can}$ be reached. This allows study possible substructures οf quarks and leptons, actually just one of the three quarks of the proton collide with the electron [1]. The electroweak interaction can be carefully studied and measurements done at  $e^-e^+$  colliders can be extended. Currently, it is a point of discussion, whether HERA can be used for heavy quark production. The discovery limit for the mass of the top quark is around 70 MeV [2].

Fig. 1.1 shows the H1 detector layout. Collisions that occur on the beam axis produce secondary particles, which should be observed by the detector. It consists mainly of two parts: calorimeters, which are used to determine energies deposited in them, and tracking detectors, which should help to examine particle tracks. Part of the latter are multi wire proportional chambers (MWPCs). The detector is not symmetrical around the interaction point, since, due to the given e and p energies, the particle showers are mostly boosted into the forward region.

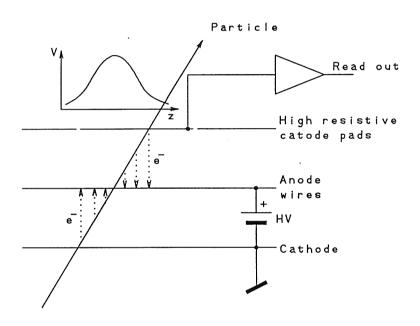

MWPCs deliver fast information (time resolution of about 20 ns) on the existence of a charged particle and give a rough estimate on one coordinate of its track with a reso-

lution of a few millimeters. Therefore, they are good candidates for first level triggers. About 2  $\mu s$  later, drift chamber data will give more accurate information on the actual track with a resolution of 100  $\mu m$ .

Fig. 1.1: H1 detector layout [3]

## 1.2 Trigger Considerations

Both electrons and protons are not spread equally over the entire ring, but kept in bunches, so that every 96 ns collisions may take place. Of course, collisions are much less frequent. The task of any trigger is therefore to determine, whether something interesting happened during a bunch crossing or not. This is done in several stages at different trigger levels with increasing selectivity.

The first trigger level, which should reduce the data rate from the initial 10 MHz to anything below 10 kHz [3] has just about 2  $\mu$ s decision time and should work 'deadtimeless'. Part of it is the z-vertex trigger, which is more extensively discussed in [4] and chapter 2.1. Once this first level accepts an event, more sophisticated examinations take place, most of which are software based. Each trigger level i+1 only decides after level i has accepted the event. Otherwise, it aborts. This procedure minimizes dead time of the detector - no further data can be taken, while trigger levels 2 and 3 analyze data. Trigger levels higher than 3 operate on multi event data buffers and do not cause further inefficiency. Finally, data are written to-tape for offline processing.

The first level trigger electronics can not rely, due to its short decision time, on software based algorithms but must be hardwired. However, to allow flexibility, one should be able to control the major parameters influencing the trigger algorithm and therefore load them into the electronics. Furthermore, computers should be able to monitor trigger performance and find defective modules.

- 10 -

#### 2. The z-Vertex Trigger

#### 2.1 Overview

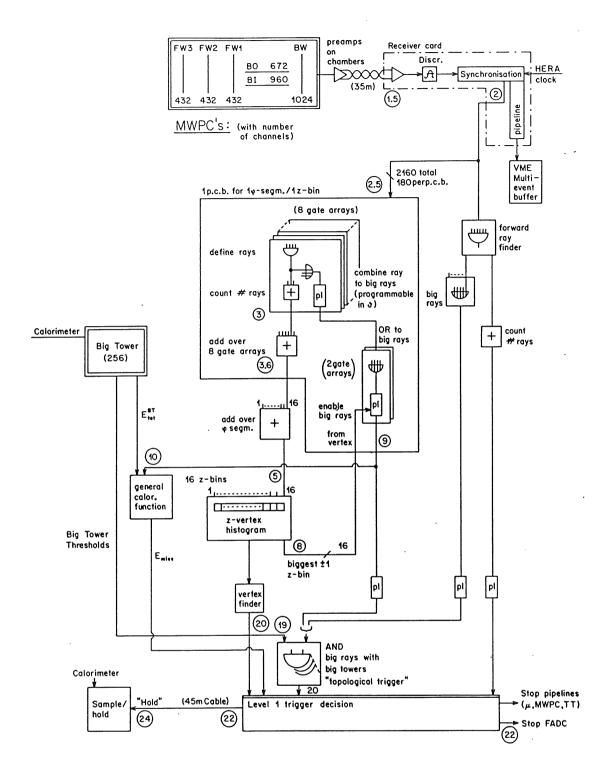

Fig. 2.1 shows a block scheme of the first level trigger logic with special emphasis given to the z-vertex trigger. Signals of at present five pairs of parallel planes of MWPCs (in future six, if a foreseen backward chamber is included) are preamplified and transferred out of the detector. Receiver cards shape and synchronize these signals against the HERA clock, which has a period of 96 ns. Then, they are made available to the z-vertex trigger electronics as well as to a forward ray finder, which will not be treated here Furthermore, the signals are all kept in a pipeline, so that they can be made available to data acquisition computers on request.

The z-vertex trigger consists of two major parts, the ray finder, which will be discussed in detail in chapter 3, and the subsequent vertex finder. The goal is, to decide, whether particles seen by the MWPCs originate from the interaction zone of the accelerator — and are therefore candidates for interesting events — or from somewhere else. In the latter case, they should be considered as background, which could, for example, be caused by a collision of beam particles with some remaining gas atoms in the beam tube. The z-vertex trigger decides on the location of the vertex of a possible event along the beam axis.

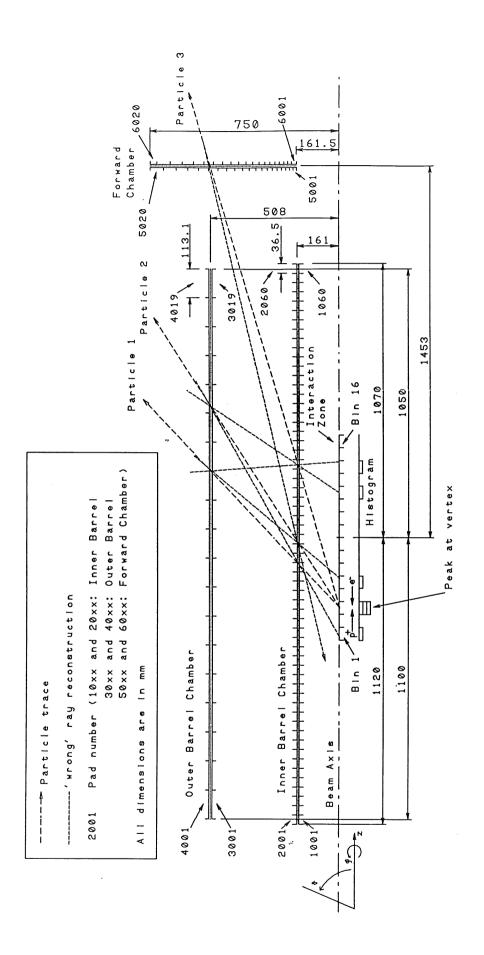

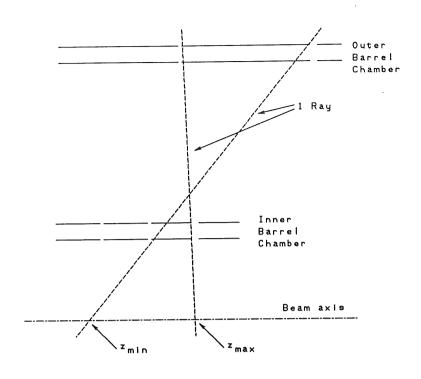

Only the inner and outer barrel chambers and the first pair of forward chambers are analyzed in the z-vertex trigger, as shown in Fig. 2.2. A particle originating from somewhere along the beam axis always crosses four chambers:

<sup>&</sup>lt;sup>1</sup> developed by Mr. H. Krehbiel, DESY Hamburg [6]

$<sup>^2</sup>$  The forward ray trigger is developed by the University of Orsay, Paris

83

Fig. 2.1: H1 first level track trigger [4]

the two innerbarrel and either the two outer barrel or the forward chambers. The projection of its track to the r-z- plane is a straight line. The hits on the four chambers can therefore be connected and tracked back to the beam axis. Of course one does not know which hits belong to a given

Fig. 2.2 MWPCs used in the z-vertex trigger

particle, so the task gets complicated. The ray finder will simply find all possible combinations of four hits, and construct a histogram of the corresponding z-coordinate for these ray candidates. In this histogram, the interaction zone along the beam axis is divided into 16 approximately 50 mm wide bins. The false rays - combinations of hits not belonging to the same particle - will produce a background in the histogram. The bin with the true vertex however will contain a peak.

It is the task of the vertex finder, to analyze, whether there is actually a peak in the histogram, indicating, that the vertex was somewhere within the interaction zone. This information will be made available to the first level trigger box, which will then make a decision based on this information as well as on data from the forward ray trigger and the calorimeter.

The z-vertex trigger can furthermore help the calorimeter trigger electronics because it indicates, into which parts of the calorimeter the rays are pointing: Once the vertex finder decided on one peak within the 16 bin wide histogram, many wrongly combined rays can be discarded. The remaining ones originate from the correct interaction area and are therefore likely to represent particles. They can be traced to the calorimeter, which is divided into 16 phi segments around the beam axis and 16 theta divisions, thus resulting in 256 so called big towers. This procedure allows to read out just a few instead of all big towers, which is hoped to substantially reduce background noise, thus allowing for lower energy thresholds. Similar combinations with a possible drift chamber trigger as suggested by H.-J. Behrend from DESY [8] are currently under consideration.

The encircled numbers in Fig. 2.1 give approximate signal propagation delays since the HERA beam crossing. The first level trigger box should decide within 22 beam

crossings (2.1  $\mu$ s = 22 x 96 ns) and produce a 'L1 keep', if the desired trigger conditions are met. However, the first trigger level differs insofar from all other levels, that it should work 'deadtimeless', which means, that a decision has to be made every 96 ns, although each one belongs to a event 2.1  $\mu$ s ago. This calls for a fully synchronously working electronic, signals belonging to the same event are nowhere allowed to have propagation delays which differ by more than 96 ns one from another.

# 2.2 Simulations of the z-Vertex Trigger

## 2.2.1 Event Data

Data available to me came in four files. They contained three different types of e-p-interactions, which were based on Lund Monte Carlo simulations by J. Gayler and background data from R. Eichlers code [4]. The detector has been simulated, using GEANT routines, by R. Eichler. An overview of the four event classes is given in table 2.1. The abbreviations will later be used to refer to the respective groups. NC stands for 'Neutral Current', CC for 'Charged Current'. The number indicates the lowest momentum transfer occuring  $(Q^2)$ . Due to the few events available to me, no effort has been made to analyze different areas of the  $Q^2$ -XBJ (X-Bjorken³) diagram separately. Background events came from the area between z=-4000 mm to z=4000 mm and were evenly distributed. Fig. 2.3 shows some examples of histograms for the four classes of events.

$<sup>^{3}</sup>$  Momentum of the quark (of the proton) interacting with the electron divided by the momentum of the entire proton.

Table 2.1: Simulated events data

| NGG100     | T . 1            |                  |        |          |      |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|------------------|------------------|--------|----------|------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NCG100     | Total event      |                  |        |          | :    | 499           |      | 0.043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            | Events with      |                  |        |          |      | 51            | •    | . 2%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                  | less             |        |          |      |               | (13  | .6%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | Avg. number      | of hi            | ts per | event    | t :  | 34.8          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | Q <sup>2</sup> X | BJ =             | 0.20   | 0.40     | 0.60 | 0.80          | 1.00 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | 667 1000         |                  | 17     | 2        |      |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | 333 667          |                  | 56     |          | 1    |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | 0 333            | GeV <sup>2</sup> | 358    | 32       | 3    | 2             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NCG1000    | Total events     | S                |        |          |      | 407           |      | anno de la companya d |

|            | Events with      | less             | than 4 | hits     | :    | 5             | (1   | . 2%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                  | less             |        |          |      |               |      | .6%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | Avg. number      |                  |        |          |      |               | ( -  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            |                  |                  | •      |          |      |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | Q <sup>2</sup> X | BJ =             | 0.20   | 0.40     | 0.60 | 0.80          | 1.00 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | 666710000        | $GeV^2$          | 8      | 1        |      |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | 3333 6667        |                  | 27     |          | 5    |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | 0 3333           |                  | 286    |          |      | 2             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                  |                  |        |          |      |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CC100      | Total events     |                  |        |          | :    | 499           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | Events with      |                  |        |          |      |               | (2.  | 2%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                  | less t           |        |          |      |               | (4.  | .0%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | Avg. number      | of hit           | s per  | event    | :    | 46.1          |      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            | Q <sup>2</sup> X | BJ =             | 0.20   | 0.40     | 0.60 | 0.80          | 1.00 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | 666710000        | GeV <sup>2</sup> | 19     | 9        | 5    | 1             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | 3333 6667        |                  | 56     | _        | _    | $\frac{1}{2}$ |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

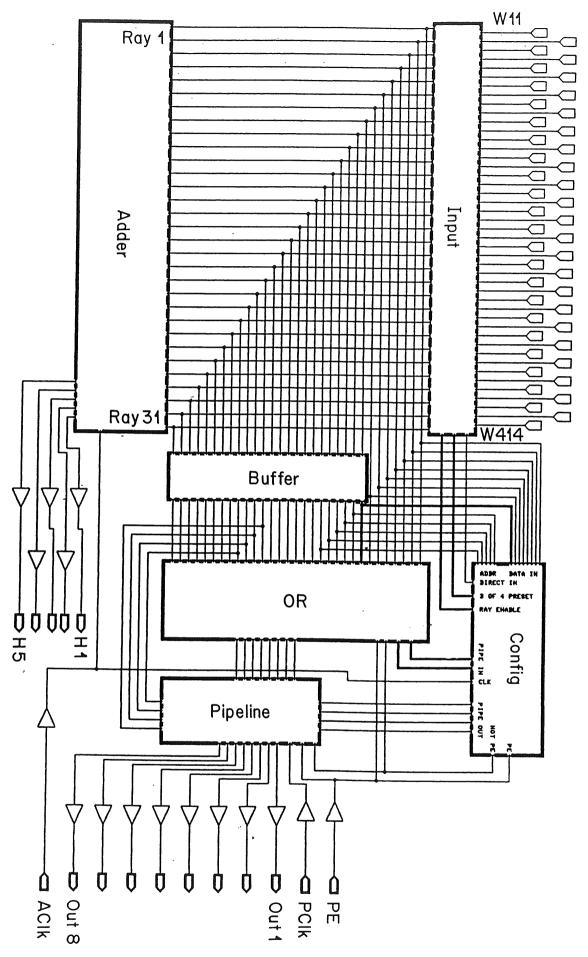

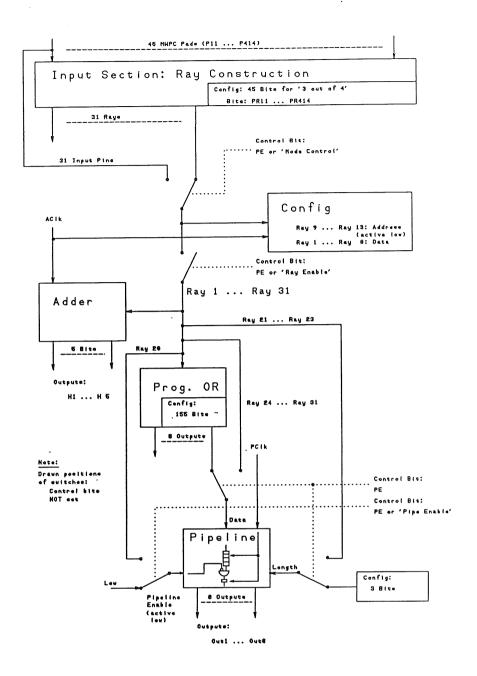

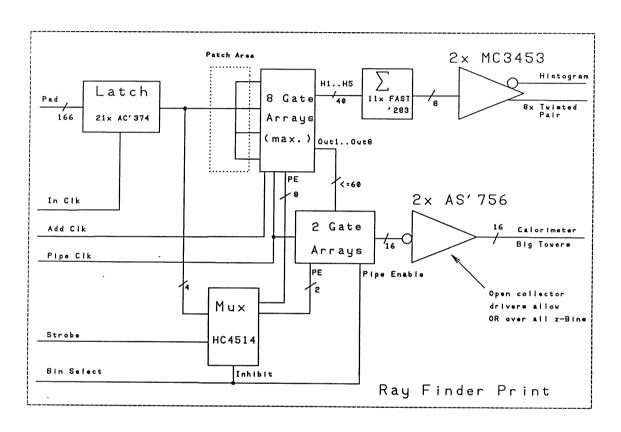

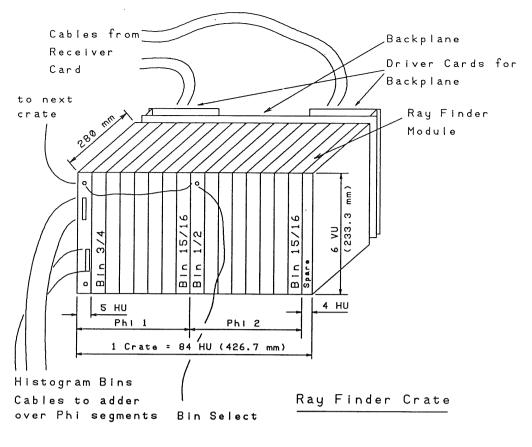

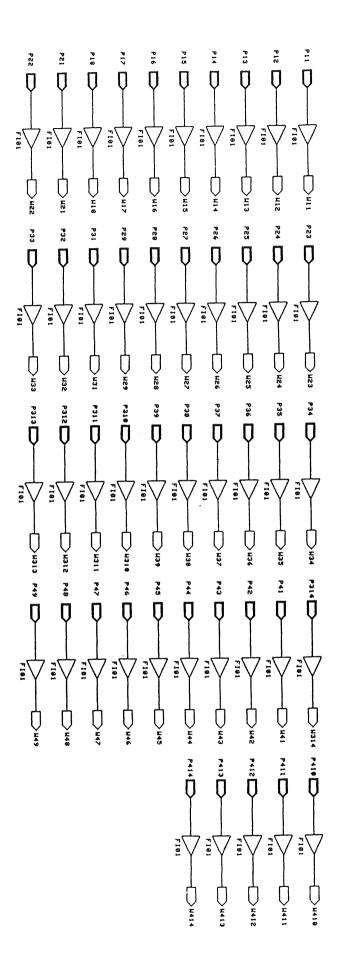

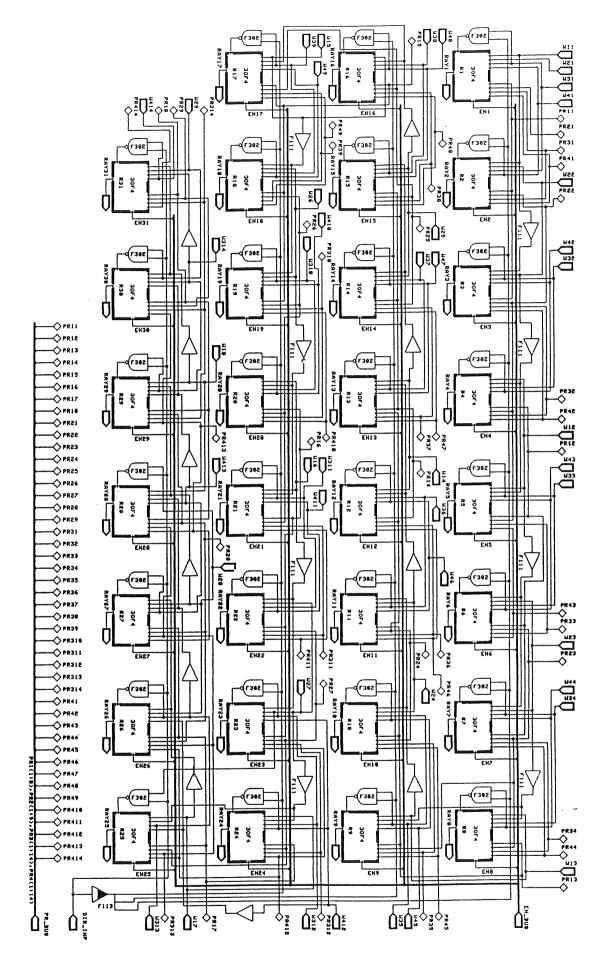

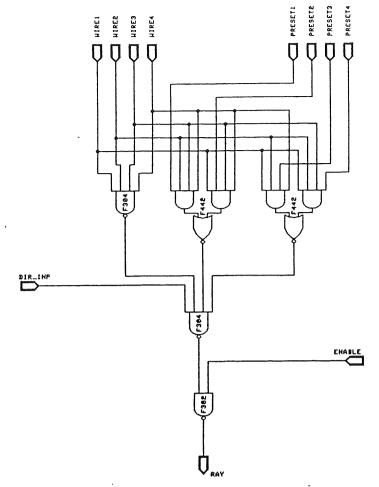

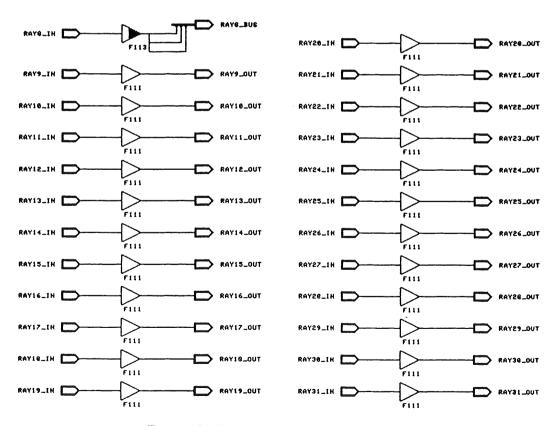

|            | 0 3333           |                  | 298    | 19<br>42 | 11   | 2             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |